# MVME135 Diagnostic Firmware User's Manual

JUNE 1988

# MVME135

## DIAGNOSTIC FIRMWARE

# USER'S MANUAL

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

VMEmodule and 135bug are trademarks for Motorola Inc.

UNIX is a registered trademark of AT&T.

Second Edition Copyright 1988 by Motorola Inc. First Edition April 1987

# TABLE OF CONTENTS

| 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 - 1                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OVERVIEW OF DIAGNOSTIC FIRMWARE                                                                                                                                                                                                                                                                                                                                                                                                | 2 - 1                                                                                             |

| 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SYSTEM START-UP                                                                                                                                                                                                                                                                                                                                                                                                                | 3 - 1                                                                                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MONITOR START-UP                                                                                                                                                                                                                                                                                                                                                                                                               | 4 - 4<br>4 - 4                                                                                    |

| 5.<br>5.1<br>5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UTILITIES                                                                                                                                                                                                                                                                                                                                                                                                                      | 5 - 1<br>5 - 1<br>5 - 1                                                                           |

| $\begin{array}{c} 6 \\ . \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 2 \\ 6 \\ . \\ 3 \\ 6 \\ . \\ 4 \\ 6 \\ . \\ 5 \\ 6 \\ . \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 2 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 5 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 6 \\ . \\ 1 \\ 1 \\ 1 \\ . \\ 1 \\ 1 \\ 1 \\ . \\ 1 \\ 1$ | GENERAL DESCRIPTION<br>HARDWARE CONFIGURATION<br>WE WRITE/READ<br>WE WRITE/READ<br>WE BYTE/WORD/LONG<br>WE MISALIGNMENT<br>WEbus SHORT I/O<br>VSB WRITE/READ<br>VSB WRITE/READ<br>VSB MISALIGNMENT<br>LOCAL DRAM LOW ADDRESS WRITE/READ<br>LOCAL DRAM LOW ADDRESS WRITE/READ<br>LOCAL DRAM WE WRITE/READ<br>LOCAL DRAM VME WRITE/READ<br>LOCAL DRAM VME WRITE/READ<br>LOCAL DRAM PARITY<br>WE TIMEOUT BERR<br>LOCAL DRAM VMSK* | 6-7<br>6-8<br>6-9<br>6-10<br>6-11<br>6-12<br>6-13<br>6-13<br>6-14<br>6-16<br>6-17<br>6-19<br>6-20 |

| 6.22 |            | VSE  | B PA           | RI    | TΥ         | BE         | ERR        | 2    | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • | 6                | -27                 |

|------|------------|------|----------------|-------|------------|------------|------------|------|------|----------|------|-----------|-----|-----|------|----|-----|-----|-----|---|-----|---|----|---|---|---|------------------|---------------------|

| 6.23 |            | VSE  | 3 TI           | ME    | 0U         | ΤB         | BER        | R    |      |          | •    | •         | •   |     | •    |    |     | •   | •   |   |     | • |    | • |   | • | 6                | -29                 |

| 6.24 |            | VSE  | 3 WR           | IT    | ΕĒ         | ERR        | ROS        |      |      |          |      |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   | 6                | -30                 |

| 6.25 | ;          | VSE  | 3 I R          | 0 1   | IAN        | NDL        | ER         | 2    |      |          |      |           |     |     |      |    |     |     |     |   |     |   | -  |   |   |   | 6                | -32                 |

| 6.26 | ;          | VSE  | 3 IR           | QN    | 1A S       | SK         |            |      |      |          | •    | •         |     |     | •    | •  |     | •   | •   | • |     |   |    |   |   |   | 6<br>6           | -33                 |

| 6.27 | ,          | VMF  | bus            | ÷۷    | S I        | /MF        | bu         | IS / | ARF  | 31-      | TF   | R         |     |     |      |    |     |     |     |   |     |   |    |   |   | • | 6                | -34                 |

| 6.28 | }          | VSE  | 3 V S          | VS    | SB         | AR         | BI         | TEI  | R    |          |      |           |     |     |      |    |     | •   |     |   | •   | • |    | • |   |   | 6                | -35                 |

| 6.29 | )          | VME  | EVS            | ٧N    | 1E         | TA         | S A        | ARB  | BIT  | ER       | 2    | •         |     |     | •    |    |     | •   |     |   |     |   |    |   |   |   | 6<br>6<br>6<br>6 | -36                 |

| 6.30 | 5          | VSE  | 3 V S          | VN    | 1E E       | bus        | 5 A        | RB:  | ITE  | R        |      |           |     |     |      |    |     |     |     | • |     | • |    |   |   |   | 6                | -38                 |

| 6.31 |            | VME  | E VS           | LC    | )CA        | AL         | AR         | BI.  | TEF  | <b>ξ</b> | OF   | R A       | Sł  | IAI | REI  | וכ | RES | 50U | JRC | Ε |     |   |    |   |   | • | 6                | -39                 |

| 6.32 | 2          | VME  | EVS            | LC    | )C A       | AL.        | AR         | BI   | TEF  | 2 F      | ŌĿ   | 8 A       | DU  | JAI |      | P0 | RT  | ED  |     |   |     |   |    |   |   |   |                  |                     |

|      |            |      | RI             | ESC   | DUF        | RCE        |            |      |      |          | •    | •         |     |     |      | •  | •   | •   |     |   | •   |   |    |   |   |   | 6                | -41                 |

| 6.33 | }          | VME  | E MP           | CS    | R/         | MP         | CSI        | 2    |      |          |      | •         |     |     |      |    |     | •   |     |   |     |   |    |   |   |   | 6                | -43                 |

| 6.34 | ŀ          | VME  | E LO           | CA    | Ľ/         | LO         | CAI        | LN   | ON   | - I      | NT   | ER        | FΕ  | RE  | NC   | Ε  | ΤE  | ST  | •   |   | •   | • | •  |   |   | • | 6                | -45                 |

| 6.35 | ;          | VSE  | 3∕VM           | 1E    | ΙŃ         | DE         | PEI        | NDE  | ENC  | E        | ΤE   | ST        |     |     | ۰.   |    | •   | •   |     |   |     |   | •  | • |   | • | 6                | -46                 |

| 6.36 | ;          | VME  | E'/VS          | SB    | IN         | DE         | PEI        | NDE  | ENC  | Ε        | ΤE   | ST        |     |     |      |    |     |     |     |   |     |   |    |   |   |   | 6                | - 47                |

| 6.37 | '          | L00  | CΆL/           | 'VM   | IE         | IN         | DEI        | PEN  | IDE  | NC       | E    | TE        | ST  |     |      |    |     |     |     |   |     |   | •. |   | • |   | 6                | -48                 |

| 6.38 | 2          | L00  | CAL/           | 'VS   | B          | IN         | DEI        | PEN  | IDE  | NC       | Ē    | ŤĒ        | ŜŤ  |     |      |    |     |     |     |   |     |   |    |   |   |   | 6<br>6<br>6<br>6 | -49                 |

|      |            |      | ,              |       | -          |            |            |      |      |          |      |           | • · |     | Ţ    | •  | •   | •   | •   | • | . • | • | •  | • | • | • | Ū                |                     |

| 7.   | M          | .680 | ð2Ø            | (0    | N          | СН         | ΙP         | ) C  | AC   | HE       | Т    | FST       | ٢S  |     |      |    |     |     |     | • |     |   |    |   |   |   |                  | 7 - 1               |

| 7.1  |            | GEN  | NÊŔA           | ۱Ì.   | DE         | SCI        | RI         | ρŢΪ  | [ ON |          |      |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | 7 - 1               |

| 7.2  |            | HAF  | RDWA           | RF    | Ē          | ON         | FI         | SUR  | RAT  | TC       | )Ň   |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | 7 - 1               |

| 7.3  |            | BAS  | SIC            | CA    | СĤ         | TN         | GT         | FS   | T    |          |      |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | 7 - 2               |

| 7.4  |            | UNI  | ĪKE            | F     | UN         | ĊТ         | ĪOI        | νČ   | ÓD   | ĒS       | T    | FSI       | г   |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | , <u>-</u><br>7 - 3 |

| 7.5  |            | DIS  | SABL           | E     | TE         | ŠŤ         |            |      |      |          |      |           |     |     |      | ÷  |     |     |     |   |     |   |    |   |   |   |                  | 7 - 4               |

| 7.6  |            | CLE  | EAR            | TE    | ŚŦ         |            |            | ÷    |      |          |      |           |     |     |      | ÷  | ÷   |     |     |   | ÷   |   |    |   |   |   |                  | 7 - 5               |

|      |            |      |                | •     |            | •          | •          | •    |      |          | •    | •         | -   | •   |      | •  | •   | -   | -   | • | Ť   | • | •  | • | • | • |                  |                     |

| 8.   | <b>C</b> 3 | 0 (  | cou            | NT    | ER         | /Τ         | ĪMI        | ER)  | T    | ES       | ΤS   |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | 8 - 1               |

| 8.1  |            | GEÌ  | NERA           | ŇL.   | DE         | śċi        | RI         | ΡTΊ  | Í ON |          |      |           |     |     |      | ÷  |     |     |     |   |     |   |    |   |   |   | :                | 8-1                 |

| 8.2  |            | HAF  | RDWA           | RE    | C          | ON         | FI         | GUR  | RAT  | IC       | )Ň   |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | 8-1                 |

| 8.3  |            | POS  | RDWA<br>ST R   | ES    | ΕŤ         | IN         | IT         | IA   | LI   | ΖĀ       | ΤI   | <b>ON</b> | T   | ES  | T    |    |     |     |     |   |     |   |    |   |   |   |                  | 8-1<br>8-2          |

| 8.4  |            | REC  | GIST           | ER    | S          | TE:        | ST         |      |      |          |      | •         |     |     | ·.   |    |     |     |     |   |     |   |    |   |   |   |                  | 8-3                 |

| 8.5  |            | cõi  | INT            | no    | WN         | TF         | ST         | •    |      |          |      |           |     |     |      | ļ  |     |     |     |   |     |   |    |   |   |   |                  | 8-4                 |

| 8.6  |            | TN   | FRR            | ΣŪΡ   | TS         | T S        | FS         | Г    |      | -        |      |           |     |     |      | ļ  |     |     |     |   |     |   |    |   |   |   |                  | 8-5                 |

| 8.7  |            | I TN | IKFF           | T     | TM         | FR         | 5 4        | M    | н7   | ċ.       | 00   | ĸ         |     |     |      | •  |     | •   | •   | • |     |   | •  | • | • | • |                  | 8-7                 |

| 8.8  |            | DES  | CRI            | рт    | τn         | N (        | ÔF         | CI   | ົດ້າ | ນໍ່ມີ    | MP   | FO        | RN  | 141 | г.   | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 8_9                 |

| 0.0  |            |      |                |       |            |            |            |      |      |          |      |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  |                     |

| 9.   | M          | MOR  | RY M           | AN    | AG         | FM         | FN.        | τи   | NT   | Т        | ( MI | MU '      | ۲ ( | FS  | ST S | :  | _   |     | _   | _ | _   | _ |    |   |   |   |                  | 9-1                 |

| 9.1  | •••        | GEN  | IFRA           | NI I  | nF         | SCI        | RTI        | ρΤI  | INN  | h        | (    |           | · · |     |      |    | •   | •   | •   | • | •   | • | •  | • | • | • |                  | <u>a_1</u>          |

| 9.2  |            | HAR  |                | RF    | č          | <b>NN</b>  | FI         | SUE  | ΔΤ   | TC       | ١Ň   | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 9-2                 |

| 9.3  |            | RP   | RFG            | 15    | TF         | R          |            |      |      |          |      | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 9-2<br>9-2          |

| 9.4  |            | TC   | REG            | 15    | ŤĒ         | R          | •          | •    | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 9-3                 |

| 9.5  |            | SIII |                | DD    | 20         | ິເ         |            | ۰F   | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 0_5                 |

| 9.6  |            | 501  |                | 'n۵   | TΔ         | 51         |            | , L  | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 9-5                 |

| 9.7  |            | WD1  |                | 7 м л |            |            |            | ς Λ1 | n D  | •••      |      |           | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 0.7                 |

| 9.8  |            |      | 11L/<br>Μ      | A D   |            | חם         |            |      | UF   | Ac       | 1 .  | 5         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • |                  | 0.0                 |

| 9.9  |            | FIL  | יו טי          | FT    | г С.<br>11 |            |            | 'r   | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • | 9                | - 101<br>- 101      |

| 9.10 | (          | 1100 | <br>           | AT    | ~          | ້ວ         | 1 7        |      | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • | 9                | -12<br>-12          |

| 9.11 |            | 1101 | . N U<br>. D D |       | 6 9        | 57/<br>50/ | 100<br>100 |      | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • | 9                | -12                 |

| 9.12 |            |      | <u>יס</u> זר   |       | с.<br>С    | 577<br>861 | 700<br>F   | •    | •    | •        | •    | •         | •   | •   | •    | •  | •   | •   | •   | • | •   | • | •  | • | • | • | 9                | -13                 |

|      |            | 1111 |                |       | ٢.         | nu i       | L          |      |      |          |      |           |     |     |      |    |     |     |     |   |     |   |    |   |   |   |                  | -14                 |

|   | 9.13           | PAGE -<br>PAGE - | -DESC  | CUSE    | ED-B    | IT         |          | •          |     |     | •   |   |   |   |   | • |   | • |   | • | • | 9-15                         |

|---|----------------|------------------|--------|---------|---------|------------|----------|------------|-----|-----|-----|---|---|---|---|---|---|---|---|---|---|------------------------------|

|   | 9.14           | PAGE-            | -DESC  | C MOD   | ) I F Y | - B I      | Τ.       |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 9-16                         |

|   | 9.15           | SEGME            | ENT-I  | DESC    | USE     | D-B        | IT       |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 9-17                         |

|   | 9.16           | TNVAL            | ID P   | AGE     |         |            |          |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 9-18                         |

|   | 9.17           | INVAL            |        | FGMF    | NT      |            |          |            | Ī   |     |     |   | Ţ | Ţ | Ţ | Ţ | · | Ī | • | • | • | 9-18<br>9-19                 |

|   | 9.18           | WRITE            |        | TFC     | ΤDΔ     | CF.        | •••      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-20                         |

|   | 9.19           | WDITE            |        | TEC.    |         | CMF        | NT.      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-2Ø<br>9-21                 |

|   | 9.20           | WDTT             |        |         |         |            | IN I     | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-21                         |

|   | 9.20           | MUTIC            | ACCI   |         |         |            | • •      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-22                         |

|   | 9.21           | KEAU             |        | 222-1   |         |            | ·        | •          | •   | • • | •   | • | ٠ | ٠ | • | • | • | • | • | • | • | 9-24<br>9-26<br>9-27         |

|   | 9.22           | UPPER            | <-L1   | 11 I V  | IUL     | AII.       | UN       | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-26                         |

|   | 9.23           | LOWER            | <-L1   | 11 I V  | IUL     | AII.       | UN       | <b>.</b> . | •   | • • |     | • | ٠ | • | • | • | • | • | • | • | • | 9-2/                         |

|   | 9.24           | PREFE            | LICH   | ON I    | NVA     |            | -PAG     | it l       | BOU | IND | ARY | • | • | • | • | • | • | • | • | • | • | 9-28                         |

|   | 9.25           | MODIF            | -Y-B)  | et an   | ID I    | NDE.       | х.       | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-3Ø                         |

|   | 9.26           | SIXTE            | EEN-B  | BITE    | BUS     | •          | • •      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 9-31                         |

|   | 9.27           | READ/            | /MOD ] | [FY/I   | WRI     | TE C       | YCL      | E          | •   | • • | •   | • | • | • |   |   |   | • | • |   | • | 9-34                         |

|   | 9.28           | TABLE            | E WAL  | KDI     | SPL.    | AY F       | ORM      | AT         |     |     | •   | • |   |   |   | • |   |   |   |   |   | 9-34<br>9-36                 |

|   |                |                  |        |         |         |            |          |            |     |     |     |   |   |   |   |   |   |   |   |   |   |                              |

|   | 1Ø. RA         | MTES             | TS     |         |         | •          |          |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 10-1<br>10-1<br>10-1         |

|   | 10.1           | GENER            | RALD   | ESCR    | ÎPT     | TON        |          |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 10-1                         |

|   | 10.2           | HARD             | ARF    | CONF    | TGU     | RAT        | TON      |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 1ø-1                         |

|   | 10.3           | SET F            | UNCT   | TON     | con     | F          |          | Ţ          | Ţ   |     |     | • | • | • | • | • | • | • | • | • | • | 10-1<br>10-2<br>10-3         |

|   | 10.4           | CET C            | TADT   | TNC     | Ann     |            | • •      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 102                          |

|   | 10.5           | SET S            | TAD    |         |         | NL J       | <b>.</b> | •          | •   | • • | •   | • | ٠ | • | • | • | • | • | • | • | • | 1Ø-5                         |

|   | 10.5           | SEI S            | MEL    |         |         | •          | • •      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 10-5                         |

|   | 10.0           | SEI V            | TEDU   | SWI     |         | - <b>-</b> | •••      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 1Ø-6<br>1Ø-7                 |

|   |                | MAKU             |        | KE22    |         | 21         | • •      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 10-7                         |

|   | 10.8           | WALK             | ABI    | I IES   | 51.     | •          | • •      | •          | •   | • • | •   | • | ٠ | • | ٠ | • | • | • | • | • | • | 1Ø-8<br>1Ø-9                 |

|   | 10.9           | REFRE            | SHI    | EST     | • •     | •          | • •      | •          | •   | • • | •   | • | ٠ | • | • | • | • | • | • | • | • | 10-9<br>10-10                |

|   | 10.10          | RANDO            | DM PA  | TTER    | RN T    | EST        | •        | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 1Ø-1Ø                        |

|   | 10.11          | PROGE            | RAM T  | EST     | • •     | •          |          | •          | •   |     | •   | • |   |   | • |   | • | • | • | • | • | 1Ø-12                        |

|   | 1Ø.12          | TAS T            | EST    | • •     | • •     | •          |          | •          | •   | •   | •   | • | • | • | • |   | • |   |   |   |   | 1Ø-14                        |

|   | 1Ø.12<br>1Ø.13 | ADDRE            | ESS C  | OMPL    | .EME    | NT         | TEST     |            | •   |     |     | • |   |   | • | • | • | • | • |   |   | 1Ø-15                        |

|   | 10.14          | BYTE/            | /WOR[  | )/LOI   | NG P    | ERM        | UTA'     | TIC        | )NS | TE  | ST  |   |   |   |   |   |   |   |   |   |   | 10-16                        |

|   | 10.15          | MEMOR            | RY ER  | ŔOR     | DIS     | PLA        | Y FO     | RM/        | AT  |     |     |   |   |   |   |   |   |   |   |   |   | 10-17                        |

|   |                |                  |        |         |         |            |          |            |     |     |     | • | • | • | • | • | • | • | • | • | • |                              |

|   | 11. MC         | 68681            |        | RT (    | 012     | ۱ Т F      | 272      |            |     |     |     |   |   |   |   |   |   |   |   |   |   | 11-1                         |

|   | 11.1           | GENER            |        | FSCA    | TPT     | TON        |          | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-1                         |

|   | 11.2           | HARD             |        | CONE    | TCU     | DAT        | TON      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-1                         |

|   | 11.2           | DATA             |        | ATC     | TEC     | T          | 100      | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-1                         |

|   | 11.5           | DAID             | DATE   | TEC     | TES     | 1          | • •      | •          | •   | • • | •   | • | ٠ | • | • | • | • | • | • | • | • | 11-3                         |

|   | 11.4           | BAUD             | KAIE   | IES     |         |            | ••       | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-3<br>11-4<br>11-5<br>11-7 |

|   | 11.5           | 1X/R             | ( REA  | DYI     | RQI     | ESI        | •        | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-5                         |

|   | 11.6           | IX/R             | ( REA  | DYI     | EST     | •          | ••       | •          | •   | • • | •   | • | • | • | • | • | • | • | • | • | • | 11-7                         |

|   | 11./           | F1F0             | FULL   | IES     | ۱.      | •          |          | •          |     |     | •   |   |   |   | • | • |   |   |   |   |   | 11-8                         |

|   | 11.8           | BREAK            | ( TES  | т.      | • •     | •          | • •      | •          | •   |     | •   | • | • | • | • | • | • | • | • | • | • | 11-9                         |

|   | 11.9           | SIO T            | IMER   | TES     | т.      | •          |          | •          | •   |     | •   | • | • | • |   | • | • |   | • | • | • | 11-9<br>11-1Ø                |

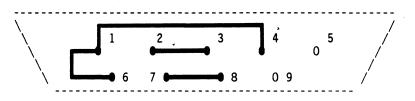

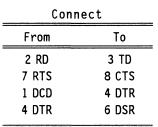

|   | 11.1Ø<br>11.11 | EXTER            | RNAL   | TX/R    | ХТ      | EST        |          |            |     |     | •   | • | • | • |   | • |   |   |   |   | • | 11-11                        |

|   | 11.11          | HANDS            | SHAKE  | E LIN   | E T     | EST        |          | •          |     |     | •   |   |   | • |   |   |   |   |   |   |   | 11-12                        |

| ¢ |                |                  |        |         |         |            |          |            |     |     |     |   |   |   |   |   |   |   |   |   |   |                              |

|   | 12. DY<br>12.1 | NAMIC            | RAM    | MEZ     | ZAN     | INE        | BOA      | RD         | ΤE  | STS | ; . |   |   |   |   |   |   |   |   |   |   | 12-1                         |

|   | 12.1           | GENEF            | RALD   | ESCR    | IPT     | ION        |          |            |     |     |     |   | - |   |   |   |   |   |   |   |   | 12-1                         |

|   | 12.2           | HARD             | ARF    | CONF    | IGU     | RAT        | ION      |            |     |     |     |   | • |   |   |   |   | - | - | - |   | 12-2                         |

|   |                |                  |        | ~ ~ 111 |         |            |          |            | •   |     | •   | • | • | • |   | - |   |   | • |   | • |                              |

| 12<br>12<br>12<br>12<br>12<br>12                         | .4<br>.5<br>.6<br>.7 -<br>.8<br>.9<br>.10<br>.11<br>.12<br>.13<br>.14<br>.15                                               | ROW MAI<br>MARCH /<br>WALK A<br>RANDOM<br>REFRES<br>PROGRA<br>TAS TE:<br>ADDRES<br>BYTE/W<br>WRITE/<br>WRITE-<br>PARITY<br>MEZZAN | BIT<br>PATT<br>H TES<br>M TES<br>ST<br>S COM<br>ORD/<br>READ<br>WRON<br>MARC<br>INE F                                                               | TEST<br>FERN<br>ST<br>ST<br>UPLE<br>LONG<br>CSR<br>G PA<br>CH TE<br>PHYS                                               | TEST<br>MENT<br>PERM<br>TEST<br>RITY<br>ST<br>ICAL                                     | TEST<br>IUTA<br>TEST               |                                 | DNS<br>SPL       | TE               | ST        | •<br>•<br>•<br>•<br>• | •<br>•<br>•<br>•<br>•<br>•            | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • | · · · · · · · · · · · · · · · · · · ·  | •<br>•<br>•<br>•<br>•<br>•            | •<br>•<br>•<br>•<br>•<br>• | •<br>•<br>•<br>•<br>•<br>•            | 12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-15<br>12-15<br>12-17<br>12-19<br>12-21                                                                           |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|---------------------------------|------------------|------------------|-----------|-----------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|---|----------------------------------------|---------------------------------------|----------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13 | .12<br>.3<br>.4<br>.5<br>.6<br>.7<br>.8<br>.9<br>.10<br>.11<br>.12<br>.13<br>.14<br>.15<br>.16<br>.17<br>.18<br>.19<br>.20 | DISPLA<br>CLEAR I                                                                                                                 | RE CC<br>STS<br>sts<br>DISPL<br>RCH T<br>PATH<br>PATH<br>H TES<br>M TES<br>ST<br>S CON<br>ORD/<br>READ<br>WRON<br>MARC<br>4 PHY<br>Y MVM<br>2 MVME2 | AY<br>AY<br>ESS<br>TEST<br>TEST<br>TEST<br>MPLE<br>CSR<br>G PA<br>CSR<br>CSR<br>CSR<br>CSR<br>CSR<br>CSR<br>CSR<br>CSR | MENT<br>TEST<br>TEST<br>TEST<br>TEST<br>TEST<br>RITY<br>EST<br>AL MA<br>4 ERR<br>ERROR | TEST<br>UTA<br>TEST<br>OR L<br>LOG | T<br>T<br>S<br>P<br>I<br>O<br>G | DNS              |                  | st        |                       | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·   | • • • • • • • • • • • • • •             |   |                                        | · · · · · · · · · · · · · · · · · · · |                            | · · · · · · · · · · · · · · · · · · · | 13 - 1<br>13 - 2<br>13 - 2<br>13 - 3<br>13 - 4<br>13 - 6<br>13 - 8<br>13 - 9<br>13 - 10<br>13 - 11<br>13 - 13<br>13 - 15<br>13 - 16<br>13 - 18<br>13 - 20<br>13 - 24<br>13 - 27 |  |

| 14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14       | .2<br>.3<br>.5<br>.6<br>.7<br>.8<br>.9<br>.1Ø                                                                              | P-CSR TI<br>GENERA<br>HARDWA<br>MPØ - M<br>SIGNAL<br>LOCATI<br>WATCH I<br>RESET<br>HALT AI<br>LOCK TI<br>GLOBAL                   | RE CC<br>IP3, /<br>ON MC<br>DOG T<br>AND H<br>ND HO<br>RANSF<br>RESE                                                                                | ONFI<br>AND<br>HIG<br>ONIT<br>IMEF<br>OLD<br>LD T<br>ER T<br>ET TE                                                     | GURAT<br>MP_CO<br>H PRI<br>OR (K<br>TEST<br>EST<br>EST<br>EST<br>EST                   | MM T<br>ORIT<br>ING)<br>[S.        | AS<br>TY<br>)3-                 | TE<br>INT<br>Ø T | ST<br>ERF<br>EST | RUP<br>rs | T I                   | rës                                   |                                         | •<br>•<br>•<br>•<br>•                   |   | • •<br>• •<br>• •<br>• •<br>• •<br>• • | •<br>•<br>•<br>•<br>•                 | •<br>•<br>•<br>•<br>•      | •<br>•<br>•<br>•<br>•                 | 14-1<br>14-2<br>14-3<br>14-5<br>14-8<br>14-11<br>14-13<br>14-14<br>14-16                                                                                                        |  |

| 15<br>15                                                 | . ト.<br>.1                                                                                                                 | INAL AS:<br>GENERA                                                                                                                | T DES                                                                                                                                               | LY IE<br>SCRI                                                                                                          | SIS<br>PTION                                                                           | •••                                | •                               | •                | •••              | •         | •                     | •                                     | •                                       | •                                       | • | •••                                    | •                                     | •                          | •                                     | 15-1<br>15-1                                                                                                                                                                    |  |

| 15.2 | HARDWARE CONFIGURATION        | 15-1 |

|------|-------------------------------|------|

| 15.3 | FAT135 (SYSTEM TEST)          | 15-3 |

|      | FAT136 (SYSTEM TEST)          |      |

| 15.5 | FATPKGØ (BOARD TEST)          | 15-5 |

| 15.6 | FATPKG1 (BOARD TEST)          | 15-6 |

| 15.7 | FAT224 (EXTERNAL MODULE TEST) | 15-7 |

|      |                               |      |

|      |                               |      |

|      |                               |      |

# LIST OF FIGURES

| FIGURE 4-1.  | MONITOR DIRECTORY STRUCTURE        | • | • | • | • | •   | • | • | 4 - 2 |

|--------------|------------------------------------|---|---|---|---|-----|---|---|-------|

| FIGURE 8-1.  | SAMPLE CIO REGISTER DUMP           | • | • | • | • | •   | • | • | 8 - 9 |

| FIGURE 9-1.  | SAMPLE TABLE WALK DISPLAY          | • | • | • | • | •   | • | • | 9-36  |

| FIGURE 1Ø-1. | SAMPLE MEMORY ERROR DISPLAY        | • | • | • | • | •   | • | • | 1Ø-17 |

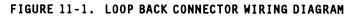

| FIGURE 11-1. | LOOP BACK CONNECTOR WIRING DIAGRAM | 1 | • | • | • | • . | • | • | 11-2  |

|              |                                    | , |   |   |   |     |   |   |       |

# LIST OF TABLES

| TABLE 6-1.  | VMEbus AND VSB TESTS 6-2                  |

|-------------|-------------------------------------------|

| TABLE 7-1.  | MC68Ø2Ø CACHE DIAGNOSTIC TESTS            |

| TABLE 8-1.  | CIO DIAGNOSTIC TESTS                      |

| TABLE 8-2.  | CIO REGISTERS                             |

| TABLE 9-1.  | MEMORY MANAGEMENT UNIT DIAGNOSTICS 9-1    |

| TABLE 9-2.  | SAMPLE TABLE WALK DISPLAY                 |

| TABLE 10-1. | MEMORY DIAGNOSTIC TESTS                   |

| TABLE 11-1. | MC68681 DUART (SIO) TESTS                 |

| TABLE 12-1. | DYNAMIC RAM MEZZANINE BOARD TESTS 12-1    |

| TABLE 13-1. | DYNAMIC MEMORY BOARD TESTS - MVME224 13-1 |

| TABLE 14-1. | MP-CSR TESTS                              |

| TABLE 15-1. | FINAL ASSEMBLY TESTS                      |

# CHAPTER 1 SCOPE

This diagnostic manual contains information about the operation and use of the MVME135 Diagnostic Firmware Package, hereafter referred to as the **diagnostics**. Chapters 3 and 4 give the user guidance in setting up the system and invoking the various utilities and tests. Chapter 5 describes utilities available to the user. Chapters 6 through 14 are guides to using each test. Chapter 15 provides the Final Assembly Tests (FAT) for the MVME135. THIS PAGE INTENTIONALLY LEFT BLANK.

1

# CHAPTER 2 OVERVIEW OF DIAGNOSTIC FIRMWARE

The MVME135 diagnostic firmware package consists of two  $64K \times 8$  EPROMs which are plugged into the MVME135 module. These two EPROMs (which may also contain 135Bug) contain a complete diagnostic monitor along with a battery of utilities and tests for exercise, test, and debug of hardware in the MVME135 environment.

The diagnostics are menu-driven for ease of use. The HE command (explained fully in Chapter 4) displays a menu of all available diagnostic functions (i.e., the tests and utilities). Each test has a subtest menu which may be called using the HE command. In addition, some utilities have subfunctions and as such have subfunction menus.

# THIS PAGE INTENTIONALLY LEFT BLANK.

.

.

•

## CHAPTER 3 SYSTEM START-UP

Plug the MVME135 diagnostic ROMs into sockets U56 (even byte) and U54 (odd byte), CAREFULLY OBSERVING THE PIN 1 ORIENTATION.

Be certain that jumper block J7 has a jumper pin installed between pins 2 and 3 to accommodate 27512-type devices.

Plug in the MVME135 under test. Attach the cable from the RS-232 terminal to the "SER PORT 1" connector on the MVME135 front panel. Engage power to the chassis. The prompt should appear following the banner (refer to Chapter 4).

# THIS PAGE INTENTIONALLY LEFT BLANK.

#### CHAPTER 4 DIAGNOSTIC MONITOR

The tests described herein are called via a common diagnostic monitor, hereafter called monitor. This monitor is menu driven and provides input/output facilities, command parsing, error reporting, interrupt handling, and a multi-level directory.

# 4.1 MONITOR START-UP

When the monitor is first brought up, following power up or pushbutton reset, the following line is displayed on the diagnostic video display terminal:

> MVME135 Debugger/Diagnostics Version x.y - mm/dd/yy <Confidence Test Fail Information> <FPC Status> <PMMU Status> Local Memory Size is z Meg 135Bug>

Where x.y is the version number and revision level of the 135Bug package being used and mm/dd/yy is the date of issue of the package. < Confidence Test Fail Information> is only printed out if the power-up confidence test fails. A fail code, indicating the mode of failure is displayed (a list of fail codes and their meaning is given in an appendix of the 135Bug Manual). < FPC Status> is the results of a floating point coprocessor check done at each power-up or reset. < PMMU Status> is the results of a check for an installed PMMU, also done at power-up or reset. The local memory size, z, will be either 1Mb or 4Mb.

At the prompt, enter SD to switch to the diagnostics directory. Command SD is explained in detail in section 4.5. The prompt should now read 135Diag>.

#### 4.2 COMMAND ENTRY AND DIRECTORIES

Entry of commands is made when the prompt 135Diag> appears. The name of the command is entered before pressing RETURN. Multiple commands may be entered. If a command expects parameters and another command is to follow it, separate the two with an exclamation mark "!". For instance, to invoke the commands MT A and MT B, the command line would read MT A ! MT B. Spaces are not required but are shown here for legibility.

Most commands consist of a command name that is listed in a main (root) directory and a subcommand that is listed in the directory for that particular command. In the main directory are commands like **BUS** and **MMU**. These commands are used to refer to a set of lower level commands.

To call up a particular bus test, one would enter (on the same line) **BUS A**. This command would cause the monitor to find the **BUS** subdirectory, and then to execute the command A from that subdirectory.

The diagram in Figure 4-1 is provided to illustrate the directory structure.

| Single Level Commands | HE<br>LE | Help<br>Loop on Error                                                                      |

|-----------------------|----------|--------------------------------------------------------------------------------------------|

| Two Level Commands    | CIO A    | Z8Ø36 Counter/Timer<br>A Post Reset Initiate                                               |

|                       | MMU A    | Memory Management Board<br>A RP Register                                                   |

| Three Level Commands  | MMU Z Ø  | Memory Management Board<br>Z 16-bit Bus<br>Ø User - Prog Space<br>1 Page - Desc Modify Bit |

# FIGURE 4-1. MONITOR DIRECTORY STRUCTURE

# 4.3 HELP - Command HE

On line documentation has been provided in the form of a HELP command (syntax: HE). This command will display a menu of the top level directory if no parameters are entered, or a menu of each subdirectory if the name of that subdirectory is entered. For example, to bring up a menu of all the bus tests, one would enter HE BUS. When a menu is too long to fit on the screen, it will pause until the operator presses RETURN.

#### 4.4 SELF-TEST - Prefix ST

The monitor provides an automated test mechanism called self test. Entering ST before a command will cause the monitor to run the tests included in an internal self test directory. ST without any parameters will run most of the MVME135 diagnostics, including those that expect special test configurations (i.e., a second MVME135, a RS-232C loopback connector, etc). Clearly, this should not be done in most situations. To facilitate testing a MVME135 in combination with only a MVME204, two Final Assembly Tests (FATs) have been provided: FATPKGØ for a MVME135 and FATPKG1 for a MVME136. Refer to the Final Assembly Test chapter for details. To run most of the SIO tests, one would enter ST SIO. Entering ST MMU Z would cause the monitor to run the three subtests (16-bit bus) for MMU Z.

Each test that is not included in the self test chain for that particular command is listed in the section pertaining to the command (i.e., refer to the Bus Test chapter for the **BUS** commands that are not in the self test chain).

#### 4.5 SWITCH DIRECTORIES - Command SD

To leave the diagnostic directory (and disable the diagnostic tests), enter SD. At this point, only the commands for 135Bug will function. To return to the diagnostic directory, the command SD is entered again. When in the 135Bug directory, the prompt will read 135Bug>. When in the diagnostic directory, the prompt will read 135Diag>. The purpose of this feature is to allow the end user to access 135Bug without the diagnostics being visible.

#### 4.6 DISPLAY ERROR COUNTERS - Command DE

Each test or command in the diagnostic monitor has an individual error counter. As errors are encountered in a particular test, that error counter will be incremented. If one were to run a self test or just a series of tests, the results could be broken down as to which tests passed by examining the error counters. **DE** will display the results of a particular test if the name of that test follows **DE**. Only non-zero values are displayed.

### 4.7 ZERO ERROR COUNTERS - Command ZE

The error counters originally come up with the value of zero, but it is occasionally desirable to reset them to zero at a later time. This command will reset all of the error counters to zero. The error counters can be individually reset by entering the specific test name following the command. Example: **ZE BUS A** will clear the error counter associated with **BUS A**.

#### 4.8 NON-VERBOSE MODE - Prefix NV

Some diagnostics will display a substantial amount of data if an error is displayed. To avoid the necessity of watching the scrolling display, a mode is provided that suppresses all messages except "PASSED" or "FAILED". This mode is called "nonverbose" and is invoked prior to calling a command by entering NV. NV ST SIO would cause the monitor to run the SIO self test, but only show the names of the subtests and the results (pass/fail).

## 4.9 LOOP CONTINUOUS MODE - Prefix LC

To repeat a test or series of tests endlessly, the prefix LC is entered. This loop will include everything on the command line. To break the loop, press BREAK. Certain tests disable the BREAK key interrupt, so pressing the ABORT or RESET buttons may become necessary.

#### 4.10 LOOP ON ERROR MODE - Prefix LE

Occasionally, when a scope or logic analyzer is in use, it becomes desirable to repeat a test endlessly at the point where an error is detected. LE accomplishes that for most of the tests. To invoke LE, enter it before the test that is to run in "loop on error" mode.

# 4.11 DISPLAY PASS COUNT - Command DP

A count of the number of passes in loop continuous mode is kept by the monitor. This count is displayed with other information at the conclusion of each pass (refer to section 4.9). To display this information without using LC, enter DP.

#### 4.12 ZERO PASS COUNT - Command ZP

Invoking this command resets the pass counter (described in section 4.11) to zero. This is frequently desirable before typing in a command that invokes the loop continuous mode. Entering this command on the same line as **LC** will result in the pass counter being reset every pass.

# CHAPTER 5 UTILITIES

The monitor is supplemented by several utilities that are separate and distinct from the monitor itself and the diagnostics.

## 5.1 WRITE LOOP - Command WL.size

The "WL.size" command invokes a streamlined write of specified size to the specified memory location. This command is intended as a technician aid for debug once specific fault areas are identified. The write loop is very short in execution so that measuring devices such as oscilloscopes may be utilized in tracking failures.

The size of the command may be specified as B for byte, W for word, or L for longword.

The command requires two parameters: target address and data to written. The address and data are both hexadecimal values and must be preceded by a  $\emptyset$  if the first digit is other than  $\emptyset$  to 9, i.e., \$FF would be entered as **OFF**. To write \$ $\emptyset\emptyset$  out to address \$FFFB $\emptyset\emptyset$ 3 $\emptyset$ , one would enter "WL.B  $\emptyset$ FFFB $\emptyset\emptyset$ 3 $\emptyset$   $\emptyset\emptyset$ ". Omission of either or both parameters will cause prompting for the missing values.

# 5.2 READ LOOP - Command RL.size

The "RL.size" command invokes a streamlined read of specified size from the specified memory location. This command is intended as a technician aid for debug once specific fault areas are identified. The read loop is very short in execution so that measuring devices such as oscilloscopes may be utilized in tracking failures.

The size of the command may be specified as B for byte, W for word, or L for longword.

The command requires one parameter: target address. The address is a hexadecimal value. To read from address \$FFFBØØ3Ø, one would enter "RL.B FFFBØØ3Ø". Omission of the parameter will cause prompting for the missing value.

5-1

THIS PAGE INTENTIONALLY LEFT BLANK.

.

•

#### CHAPTER 6 VMEbus AND VSB TESTS

## 6.1 GENERAL DESCRIPTION

This section details the diagnostics provided to test the VMEbus and VSB interfaces. Table 6-1 lists the VMEbus and VSB tests.

The bus tests are divided into groups zero through five. These groupings correspond to the type of testing done. In type-Ø tests, the UUT (Unit Under Test) performs data transfers through various bus interfaces (local bus, VMEbus, VSB) to slaves. This mainly tests the buffers going to the bus. No other bus master is allowed to use the bus being tested while a test is running.

The type-1 tests verify the functioning of bus hardware used for purposes other than normal data transfers. This includes interrupt circuitry, bus-related control, and status registers, etc. For some of these tests an Aux (Auxiliary bus-master) is required. The other MVME135 board in the chassis is used for this purpose.

All of the type-2 tests require an Aux board. In these tests, the UUT performs data transfers to slaves over the various interfaces. While this is going on, the Aux attempts to access the same slave that the UUT is accessing by writing/reading to it over the same interface that the UUT is using. The activity of the Aux and the UUT are synchronized so that they are both accessing the same slave at the same time. This tests the timing chains and circuitry involved with back-to-back accesses with another master (i.e., can the Aux take the bus from the UUT, can the UUT take the bus back from the Aux again?).

In the type-3 tests, the UUT accesses slaves using the various interfaces. While the UUT is accessing a slave, the Aux attempts to access the same slave using a different interface.

The type-4 tests have the UUT doing accesses to a slave while at the same time the Aux does accesses to some other slave using the same interface that the UUT is using.

The type-5 tests, referred to as independence tests, consist of accesses to a slave over a particular interface during simultaneous accesses to a different slave over a different interface by the Aux.

Some tests require the simultaneous execution of two bus masters, the UUT and the Aux. In these situations, the UUT must force the Aux to execute code for the test. To do this, first the UUT downloads the code that the Aux is to execute from the UUT EPROM into the Aux's onboard DRAM. The UUT then writes a vector into the Aux's vector table which points at the code which was downloaded. The UUT then sets up a "packet" (predefined data structure for passing information from UUT to Aux and vice-versa) and uses the MVMEØ5Ø to interrupt the Aux master with a VMEbus level 7 interrupt. The Aux vectors into the downloaded code and is instructed to read a field in the packet to get a command number. Using the command number, the Aux indexes into a jump table and jumps to the code for the particular test.

# 6.2 HARDWARE CONFIGURATION

The following hardware is required to perform these tests.

MVME135 CPU - Board being tested (referred to as the "UUT"). MVME135 CPU - Auxiliary bus master ("Aux") used in some tests. MVME2Ø4 RAM Board - Addressed at \$ØØAØØØØØ (VMEbus) and \$ØØCØØØØØ (VSB). MVMEØ5Ø System Module - Used to generate VMEbus interrupts. Video Display Terminal.

See Chapter 15 (Final Assembly Tests) for a more thorough description of system setup requirements, including jumper placements, etc.

| Monitor Command | Title                                 | Section |

|-----------------|---------------------------------------|---------|

| BUS Ø.A         | VME Write/Read                        | 6.3     |

| BUS Ø.B         | VME Byte/Word/Long                    | 6.4     |

| BUS Ø.C         | VME Misalignment                      | 6.5     |

| BUS Ø.D         | VME Short I/O                         | 6.6     |

| BUS Ø.E         | VSB Write/Read                        | 6.7     |

| BUS Ø.F         | VSB Byte/Word/Long                    | 6.8     |

| BUS Ø.G         | VSB Misalignment                      | 6.9     |

| BUS Ø.H         | Local Dram base Ø Write/Read          | 6.1Ø    |

| BUS Ø.I         | Local Dram base \$FFEØØØØØ Write/Read | 6.11    |

| BUS Ø.J         | Local Dram VME Write/Read             | 6.12    |

| BUS 1.A         | SYSFAIL IRQ                           | 6.13    |

| BUS 1.B         | LBTO BERR                             | 6.14    |

| BUS 1.C**       | Local Dram Parity BERR                | 6.15    |

| BUS 1.D         | VME Timeout BERR                      | 6.16    |

| BUS 1.E         | Local Dram VMSK*                      | 6.17    |

| BUS 1.F         | VME Slave BERR                        | 6.18    |

#### TABLE 6-1. VMEbus AND VSB TESTS

| Monitor Command | Title                              | Section |

|-----------------|------------------------------------|---------|

| BUS 1.G         | VME Interrupt Handler              | 6.19    |

| BUS 1.H         | VME IRQ Mask                       | 6.2Ø    |

| BUS 1.I         | VME Broadcast IRQ                  | 6.21    |

| BUS 1.J         | VSB Parity BERR                    | 6.22    |

| BUS 1.K         | VSB Timeout BERR                   | 6.23    |

| BUS 1.L         | VSB Write Error                    | 6.24    |

| BUS 1.M         | VSB Interrupt Handler              | 6.25    |

| BUS 1.N         | VSB Interrupt Mask                 | 6.26    |

| BUS 2.A         | VME vs VME Arbiter                 | 6.27    |

| BUS 2.B         | VSB vs VSB Arbiter                 | 6.28    |

| BUS 2.C         | VME vs VME TAS Arbiter             | 6.29    |

| BUS 3.A         | VME vs VSB Arbiter                 | 6.3Ø    |

| BUS 3.B         | VME vs Local Arbiter (SHARED)      | 6.31    |

| BUS 3.C         | VSB vs Local Arbiter (DUAL-PORTED) | 6.32    |

| BUS 4.A         | VME MPCSR/MPCSR                    | 6.33    |

| BUS 4.B         | VME Local/Local                    | 6.34    |

| BUS 5.A         | VSB/VME Independence               | 6.35    |

| BUS 5.B         | VME/VSB Independence               | 6.36    |

| BUS 5.C         | Local/VME Independence             | 6.37    |

| BUS 5.D         | Local/VSB Independence             | 6.38    |

TABLE 6-1. VMEbus AND VSB TESTS (cont.)

**\*\*** Not in self-test chain.

#### 6.3 VME WRITE/READ

#### BUS Ø.A

6.3.1 Description

This command is a write/read test to RAM via VMEbus. The test writes a pattern and then reads it back, comparing the data read to the expected value.

6.3.2 Command Input

135Diag>BUSØ.A

#### 6.3.3 Response/Messages

After entering this command, the following should be printed out:

Ø.A VME Write/Read ......

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

| Ø.A | VME Write/Read |                 | Running>     |

|-----|----------------|-----------------|--------------|

|     | Addr=ØØAØ1234  | Expect=ØØØØ5678 | Read=FFFFFFF |

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.A VME Write/Read ..... PASSED

#### 6.4 VME BYTE/WORD/LONG

# 6.4.1 Description

This command is a test that writes a pattern of bytes to VMEbus memory and then reads back the data in both words and longwords to verify the byte/word/long addressing.

6.4.2 Command Input

135Diag> BUS Ø.B

# 6.4.3 Response/Messages

After entering this command, the following should be printed out:

Ø.B VME Byte/Word/Long ......Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

Ø.B VME Byte/Word/Long .....Running ----->

Addr=ØØAØ1234 Expect=ØØØØ4567 Read=FFFFFFF

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.B VME Byte/Word/Long ..... Running -----> PASSED

# 6.5 VME MISALIGNMENT

# BUS Ø.C

#### 6.5.1 Description

This command tests the ability of the VMEbus interface to write/read longwords to/from odd addresses. The test also writes bytes and word out to odd addresses.

# 6.5.2 Command Input

135Diag> BUS Ø.C

#### 6.5.3 Response/Messages

After entering this command, the following should be printed out:

Ø.C VME Misalignment ......Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

| Ø.C | VME Misalignment | • • • • • • • • • • • • • • • • • • • • | Running>     |

|-----|------------------|-----------------------------------------|--------------|

|     | Addr=ØØAØØØØ4    | Expect=ØØØØ4567                         | Read=FFFFFFF |

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.C VME Misalignment ..... Running -----> PASSED

BUS Ø.D

# 6.6 VMEbus SHORT I/0

#### 6.6.1 Description

This command tests the VMEbus short I/O addressing space access by testing a bit in the MVME204 control/status register. The location of the register is within the short I/O addressing space. This test preserves the contents of the control/status register and restores it before returning control to the diagnostic monitor.

6.6.2 Command Input

135Diag> BUS Ø.D

#### 6.6.3 Response/Messages

After entering this command, the following should be displayed:

Ø.D VME Short I/O ......Running ------>

If the bit in the MVME204 control/status register cannot be set, then the error is reported in the following manner:

Ø.D

VME Short I/O

Running

Addr=FFFFBEØ1

Expect=ØØØØØØØ

Read=ØØØØØØØØ

....

FAILED

FAILED

If the bit does get set by the test, then the test passes.

Ø.D VME Short I/O ..... PASSED

6 - 7

# 6.7 VSB WRITE/READ

#### BUS Ø.E

6.7.1 Description

This command is a write/read test to RAM via the VSB bus. The test writes a pattern and then reads it back, comparing the data read to the expected value.

6.7.2 Command Input

135Diag>BUSØ.E

#### 6.7.3 Response/Messages

After entering this command, the following should be printed out:

Ø.E VSB Write/Read .....>

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

| Ø.E | VSB Write/Read | Running>        |              |

|-----|----------------|-----------------|--------------|

|     | Addr=ØØCØ1234  | Expect=ØØØØ5678 | Read=FFFFFFF |

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.E VSB Write/Read ..... PASSED

# 6.8 VSB BYTE/WORD/LONG

# 6.8.1 Description

This command is a test that writes a pattern of bytes to the VSB bus memory and then reads back the data in both words and longwords to verify the byte/word/long addressing.

# 6.8.2 Command Input

135Diag>BUSØ.F

## 6.8.3 Response/Messages

After entering this command, the following should be printed out:

Ø.F VSB Byte/Word/Long ......Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

| Ø.F | VSB Byte/Word/I | _ong            | Running>     |  |

|-----|-----------------|-----------------|--------------|--|

|     | Addr=ØØCØ1234   | Expect=ØØØØ4567 | Read=FFFFFFF |  |

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.F VSB Byte/Word/Long ..... Running -----> PASSED

# BUS Ø.F

#### 6.9 VSB MISALIGNMENT

#### BUS Ø.G

# 6.9.1 Description

This command tests the ability of the VSB bus interface to write/read longwords to/from odd addresses. This test also writes bytes and words out to odd addresses.

# 6.9.2 Command Input

135Diag> BUS Ø.G

# 6.9.3 Response/Messages

After entering this command, the following should be printed out:

Ø.G VSB Misalignment ......Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

| Ø.G | VSB Misalignment | •••••           | Running>     |  |

|-----|------------------|-----------------|--------------|--|

|     | Addr=ØØCØ1234    | Expect=ØØØØ4567 | Read=FFFFFFF |  |

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.G VSB Misalignment .....> PASSED

6

# 6.10 LOCAL DRAM LOW ADDRESS WRITE/READ

BUS Ø.H

#### 6.10.1 Description

The local DRAM should appear at \$0 on the local bus regardless of the VMEbus address specified by the mapping switches if the OPT0 bit in control register CNT5 is set.

This command is a write/read test to local DRAM at \$0. The test writes a pattern and then reads it back, comparing the data read to the expected value.

#### 6.10.2 Command Input

135Diag> BUS Ø.H

#### 6.10.3 Response/Messages

After entering this command, the following should be printed out:

Ø.H Local DRAM low address Write/Read.....Running ------>

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

Ø.H Local DRAM low address Write/Read.....Running ----->

Addr=ØØØØ1234 Expect=ØØØØ5678 Read=FFFFFFF

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.H Local DRAM low address Write/Read.....Running -----> PASSED

## 6.11 LOCAL DRAM HIGH ADDRESS WRITE/READ

#### BUS Ø.I

6.11.1 Description

The local DRAM should appear at \$FFEØØØØØ on the local bus regardless of the VMEbus address specified by the mapping switches or the state of the OPTØ bit in control register CNT5.

This command is a write/read test to local DRAM at FE00000 via the local bus. The test writes a pattern and then reads it back, comparing the data read to the expected value.

6.11.2 Command Input

135Diag>BUSØ.I

#### 6.11.3 Response/Messages

After entering this command, the following should be printed out:

Ø.I Local DRAM High address Write/Read....Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

Ø.I Local DRAM High address Write/Read....Running ------>

Addr=FFEØ1234 Expect=ØØØØ5678 Read=FFFFFFFF

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.I Local DRAM High address Write/Read....Running -----> PASSED

# 6.12 LOCAL DRAM VME WRITE/READ

# BUS Ø.J

6.12.1 Description

The local DRAM should appear on the VMEbus at the address specified by the mapping switches. This command is a write/read test to local DRAM at that address. The OPT $\emptyset$  bit in CNT5 is cleared to assure that the local DRAM is not accessed via the local bus. The test writes a pattern and then reads it back, comparing the data read to the expected value.

6.12.2 Command Input

135Diag> BUS Ø.J

#### 6.12.3 Response/Messages

After entering this command, the following should be printed out:

Ø.J Local DRAM VME Write/Read.....Running ----->

If an error occurs, the address of the errant data will be displayed along with the expected and read values.

Ø.J Local DRAM VME Write/Read.....Running ----->

Addr=ØØØØ1234 Expect=ØØØØ5678 Read=FFFFFFF

(actual values depend on the error, each is 8 hex digits)

.... FAILED

If no errors are encountered, then the word "PASSED" will be printed out.

Ø.J Local DRAM VME Write/Read.....Running -----> PASSED

#### 6.13 SYSFAIL IRQ

# BUS 1.A

## 6.13.1 Description

This command tests the SYSFAIL interrupt request logic. The intent of the test is to verify that the MVME135 is able to generate the SYSFAIL signal as well as recognize it as an interrupt source when the signal is generated elsewhere.

The implementation of the test is as follows:

Step 1: Enable SYSFAIL IRQ.

- Step 2: Assert SYSFAIL by clearing BDFAIL bit in CNT5 control register.

- Step 3: After a short time delay, check local copy of STAT2. If the interrupt occurred, then a bit in the local copy will have been cleared in the interrupt handler. The interrupt handler negates SYSFAIL.

- Step 4: If the interrupt did not occur or the SYSFAIL bit in STAT2 is still clear, then the test fails and an error message is printed.

# 6.13.2 Command Input

135Diag> BUS 1.A

#### 6.13.3 Response/Messages

After entering this command, the following should be displayed:

1.A SYSFAIL IRQ ......

If the interrupt never occurs or the SYSFAIL bit does not get set by the interrupt handler, then the following error message will be printed out:

| 1.A | SYSFAIL IRQ   |                 | .Running>    |

|-----|---------------|-----------------|--------------|

|     | Addr=FFFBØØ32 | Expect=ØØØØØØCF | Read=ØØØØØDF |

|     | FAILED        |                 |              |

NOTE: If the "Expect" and "Read" values are identical, then the SYSFAIL bit did not get set by the interrupt handler.

6-14

If the test passes, then the display will appear as follows:

1.A SYSFAIL IRQ .....> PASSED

•

## 6.14 LBTO BERR

## BUS 1.B

#### 6.14.1 Description

This command tests the Local Bus Time-Out error circuitry and checks the status bit LCLERR\* in the MVME135 register STAT2. The test has been implemented in the following manner:

Step 1: Attempt to read from a non-existent location that will be decoded as being in the local resource map.

Step 2: If the local bus time-out bus error does not occur or status bit LCLERR\* does not get cleared, then report the error.

6.14.2 Command Input

135Diag>BUS 1.B

#### 6.14.3 Response/Messages

After entering this command, the following should be displayed:

If the bus error does not occur or the status bit LBTO does not get cleared, then the error will be reported as shown:

If the bus error occurs as planned, and the LBTO bit does get cleared, then the test passes.

1.B LBTO BERR .....> PASSED

#### 6.15 LOCAL DRAM PARITY

## BUS 1.C

6.15.1 Description

This command tests the parity generation and checking circuitry associated with the local dynamic RAM (including the parity error BERR generation circuitry).

NOTE: Parity generation/checking for the local DRAM is an option on the MVME135. In order to take advantage of this option, the local DRAM must be configured to operate with one wait state. This can be done by installing a jumper pin between pins 2 and 3 of jumper block J6. THE TEST WILL NOT RUN PROPERLY UNLESS THIS JUMPER IS INSTALLED.

This test does not appear in the standard self-test sequence (reference the **ST** command) because of the necessity to make a jumper change before running.

The test has been implemented in the following manner:

- Step 1: Assert OPTØ so that the on-board DRAM is mapped to \$Ø on the local bus.

- Step 2: For each byte of the targeted long-word, do the following...

- Enable parity error reporting by local DRAM.

- Enable write-wrong-parity (WWP) bit in CNT1.

- Do byte write to target address (with wrong parity).

- Disable WWP bit.

- Do byte read from target address.

- Check for BERR .

- Check for STAT2's RAMERR\* bit asserted.

- Step 3: If the parity fault bus error does not occur or status bit RAMERR\* does not get cleared, then report the error.

- Step 4: Negate OPTØ so that local DRAM is accessed via VMEbus and repeat steps 2 and 3.

#### 6.15.2 Command Input

135Diag> BUS 1.C

#### 6.15.3 Response/Messages

After entering this command, the following should be displayed:

1.C Local DRAM Parity ......Running ----->

If the bus error does not occur or the status bit LBTO does not get cleared, then the error will be reported as shown:

1.C Local DRAM Parity .....Running -----> Addr=FFFBØØ32 Expect=ØØØØØØDE Read=ØØØØØØDF .... FAILED

If the bus error occurs as planned, and the LBTO bit does get cleared, then the test passes.

1.C Local DRAM Parity ...... Running -----> PASSED

#### 6.16 VME TIMEOUT BERR

#### 6.16.1 Description

This command tests the ability of the MVME135 to terminate a VMEbus cycle if no slave responds by means of the VMEbus timeout generator (part of the MVME135's System Controller circuitry). This test also tests the VBER\* bit in the MVME135's STAT2 register.

The test has been implemented in the following manner:

- Step 1: Attempt to read from a location that will be decoded as being mapped to the VMEbus but where it is known that no VMEbus slave will respond.

- Step 2: If the VMEbus timeout bus error does not occur or status bit VBER\* does not get cleared, then report the error.

#### 6.16.2 Command Input

135Diag>BUS 1.D

#### 6.16.3 Response/Messages

After entering this command, the following should be displayed:

1.D VME Timeout BERR ......

If the bus error does not occur or the status bit VBER\* does not get cleared, then the error will be reported as shown:

| 1.D | VME Timeout BERR |                | Running>     |

|-----|------------------|----------------|--------------|

|     | Addr=FFFBØØ32    | Expect=ØØØØØD7 | Read=ØØØØØDF |

|     | FAILED           |                |              |

If the bus error occurs as planned, and the VBER\* bit does get cleared, then the test passes.

1.D VME Timeout BERR ..... PASSED

#### 6.17 LOCAL DRAM VMSK\*

#### BUS 1.E

#### 6.17.1 Description

This command tests the functioning of the VMSK\* bit in CNT2. When this bit is asserted the local DRAM should be inaccessible from the VMEbus. This test is in two parts. In the first part of the test the local CPU attempts to access the local DRAM via the VMEbus. In the second part of test, the other MVME135 attempts to access the local DRAM of the MVME135 under test. This test requires that the Aux MVME135 be present in the chassis.

The test has been implemented in the following manner:

Step 1: Assert VMSK\* bit in CNT2.

Step 2: Local Access

- Enable parity error reporting by local DRAM.

- Negate OPTØ bit in CNT5 (no local image of DRAM at  $\$\emptyset$ ).

- Access local DRAM via VMÉbus.

- VMEbus Timeout circuit should issue BERR.